北理工課題組在鐵電疇壁邏輯器件方面取得重要研究進(jìn)展

發(fā)布日期:2022-06-11 供稿:前沿交叉科學(xué)研究院

編輯:朱倩云 審核:唐水源 閱讀次數(shù):近日,北京理工大學(xué)前沿交叉科學(xué)研究院/材料學(xué)院王靜、黃厚兵課題組在鐵電疇壁邏輯器件方面取得重要研究進(jìn)展,與清華大學(xué)南策文教授團(tuán)隊(duì)合作,在《Nature Communications》上發(fā)表研究成果:“Ferroelectric domain-wall logic units”。該研究工作通過(guò)低電壓調(diào)控自組裝鐵電納米島中的疇壁網(wǎng)絡(luò)形態(tài),實(shí)現(xiàn)了“NOT, NAND, NOR”等7種基本邏輯門(mén)和“Fan-out”等邏輯電路,為實(shí)現(xiàn)全電子存算一體化高密度集成器件提供了設(shè)計(jì)思路和理論基礎(chǔ)。該論文第一作者為王靜副研究員和清華大學(xué)馬靜副教授,通訊作者為黃厚兵研究員和南策文教授。昆明理工大學(xué)馬吉教授,北京師范大學(xué)張金星教授,清華大學(xué)林元華教授和易迪助理教授以及賓夕法尼亞州立大學(xué)陳龍慶教授也參與了研究和討論。北京理工大學(xué)前沿交叉科學(xué)研究院/材料學(xué)院Hasnain Mehdi Jafri博士后(已出站),碩士生樊源源,楊華宇,博士生劉迪,清華大學(xué)博士生王玥,陳明鳳為合作者。

在過(guò)去的幾十年中,鐵性材料中的疇壁(DW)由于其豐富的物理現(xiàn)象和在納米電子學(xué)和自旋電子學(xué)中的潛在應(yīng)用引起了大家廣泛的研究興趣。特別值得一提的是最近基于電流或磁場(chǎng)操控鐵磁性疇壁而設(shè)計(jì)的賽道存儲(chǔ)器[Science 320, 190 (2008);Science 330, 1810(2010)]和鐵磁疇壁邏輯器件[Science 309, 1688 (2005); Nature 579, 214 (2020)]。但是,由于鐵磁性疇壁寬度較寬,而且電流或磁場(chǎng)的引入極大增加了器件的功耗,因此設(shè)計(jì)新型疇壁存儲(chǔ)器或邏輯器件迫在眉睫。因?yàn)殍F電材料具有更強(qiáng)的各向異性,所以鐵電疇壁表現(xiàn)出較窄的疇壁寬度(僅有幾納米),且鐵電疇壁電導(dǎo)的電場(chǎng)可控性也進(jìn)一步促進(jìn)了其在低功耗、高密度存儲(chǔ)器中的應(yīng)用。近年來(lái),國(guó)內(nèi)外眾多研究小組對(duì)鐵電疇壁存儲(chǔ)器件進(jìn)行了廣泛研究,但是基于鐵電疇壁的邏輯器件卻鮮有報(bào)道,這主要是因?yàn)殍F電疇壁形態(tài)的靈活、穩(wěn)定控制具有很大挑戰(zhàn)。

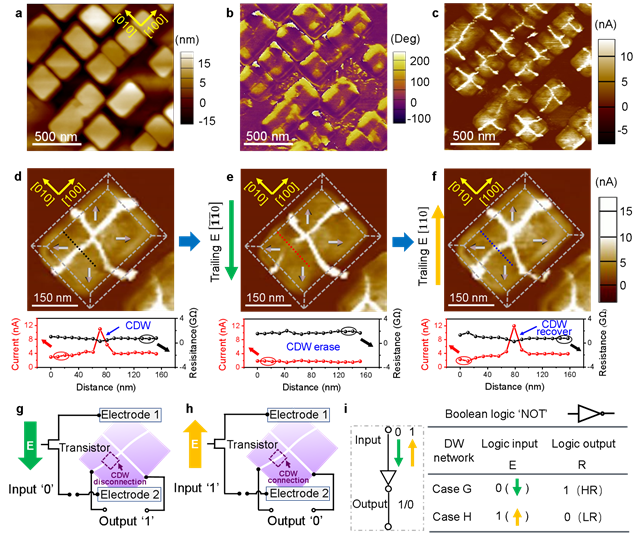

圖1 電場(chǎng)控制荷電疇壁開(kāi)關(guān)以及“非”門(mén)的設(shè)計(jì)。

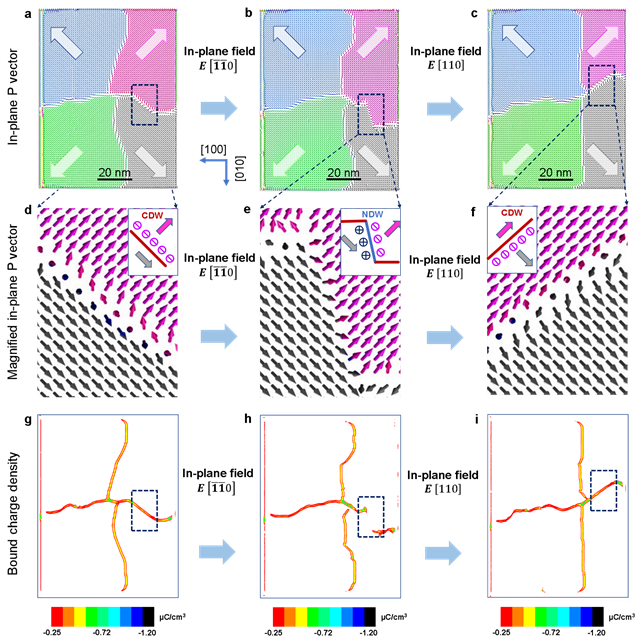

在該工作中,研究學(xué)者在自組裝 BiFeO3 納米島陣列的每個(gè)島上觀察到了十字形帶電疇壁,且得易于納米島幾何形狀對(duì)十字形帶電疇壁的拓?fù)浔Wo(hù),研究學(xué)者可以通過(guò)較小電場(chǎng)來(lái)穩(wěn)定、獨(dú)立地控制單個(gè)導(dǎo)電疇壁的連通和斷開(kāi),實(shí)現(xiàn)對(duì)單個(gè)疇壁電阻態(tài)的開(kāi)關(guān)控制。通過(guò)相場(chǎng)模擬分析,研究學(xué)者認(rèn)為導(dǎo)電疇壁的連通和斷開(kāi)伴隨著荷電疇壁和中性疇壁的相互轉(zhuǎn)化。

圖2. 基于相場(chǎng)模擬探究電場(chǎng)對(duì)荷電疇壁通斷的調(diào)控機(jī)制。

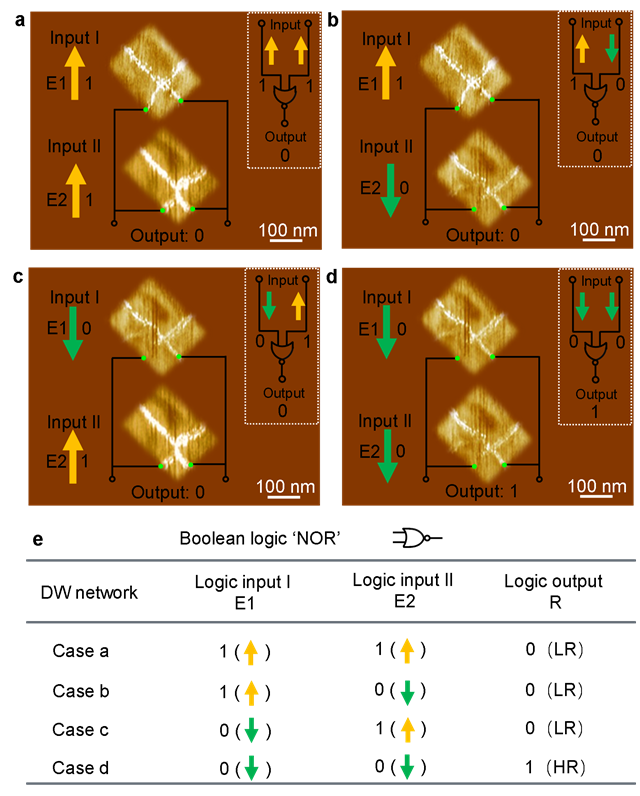

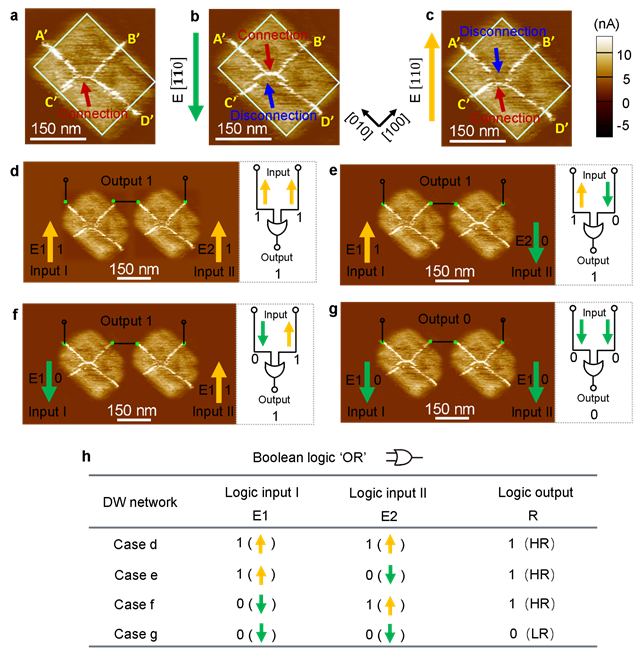

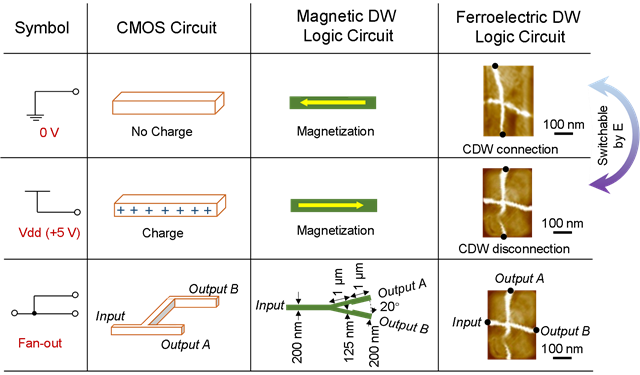

在此基礎(chǔ)上,研究學(xué)者進(jìn)一步設(shè)計(jì)了NAND,NOR等7種基本的邏輯門(mén)和“Fan-out”等邏輯電路。該工作為全電子、低功耗、高密度集成的存算一體化器件提供了設(shè)計(jì)思路和理論基礎(chǔ)。

圖3. 基于鐵電疇壁設(shè)計(jì)的“或非”邏輯門(mén)。

圖4. 基于鐵電疇壁設(shè)計(jì)的“或”邏輯門(mén)。

圖5. 鐵電疇壁邏輯電路與半導(dǎo)體CMOS、鐵磁疇壁邏輯電路的對(duì)比。

附作者簡(jiǎn)介:

王靜,北京理工大學(xué)前沿交叉科學(xué)研究院副研究員。主要從事鐵電及多鐵性復(fù)雜氧化物薄膜/異質(zhì)結(jié)的外延生長(zhǎng),疇結(jié)構(gòu)演化機(jī)理及多場(chǎng)耦合調(diào)控方面的研究。發(fā)表論文50余篇,包含Nat. Commun., Adv. Mater., Acta Mater., ACS Appl. Mater. Interfaces 等。主持國(guó)家自然科學(xué)基金青年項(xiàng)目,中國(guó)博士后項(xiàng)目,為JAD首屆青年編委。

黃厚兵,北京理工大學(xué)前沿交叉科學(xué)研究院特別研究員,博士生導(dǎo)師。主要從事相場(chǎng)模擬材料微觀結(jié)構(gòu)演化研究,在Nature, Science, Adv. Mater., Adv. Func. Mater., Acta Mater., Sci. Bull.等期刊發(fā)表SCI論文110余篇,多次在國(guó)際大會(huì)作邀請(qǐng)報(bào)告。所開(kāi)發(fā)的模型源代碼已集成于商業(yè)軟件μ-Pro。黃厚兵特別研究員先后主持自然科學(xué)基金面上、科技部重點(diǎn)研發(fā)計(jì)劃子任務(wù)等5項(xiàng)。擔(dān)任“相場(chǎng)與集成計(jì)算材料工程會(huì)議”理事會(huì)常務(wù)理事、中國(guó)硅酸鹽學(xué)會(huì)青年工作委員會(huì)委員、北京市硅酸鹽學(xué)會(huì)理事和Adv. Mater. Dev. 青年編委等。

論文詳情:

Jing Wang#, Jing Ma#, Houbing Huang*, Ji Ma, Hasnain Mehdi Jafri, Yuanyuan Fan, Huayu Yang, Yue Wang, Mingfeng Chen, Di Liu, Jinxing Zhang, Yuan-Hua Lin, Long-Qing Chen, Di Yi & Ce-Wen Nan*,F(xiàn)erroelectric domain-wall logic units, Nat. Commun. 13, 3255 (2022).

DOI: https://doi.org/10.1038/s41467-022-30983-4

論文鏈接:https://www.nature.com/articles/s41467-022-30983-4

分享到: